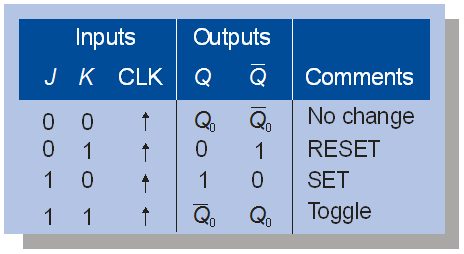

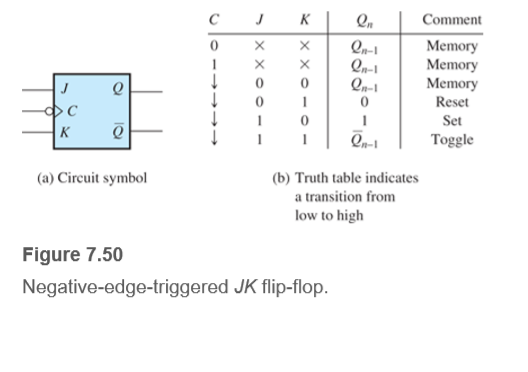

Why does the JK flip-flop toggles on the 'negative edge' of its clock input when its inputs are connected to +v (i.e when j=1 , k=1)? - Quora

digital logic - Edge triggering seems to me leaving every circuit in an inconsistent state? - Electrical Engineering Stack Exchange

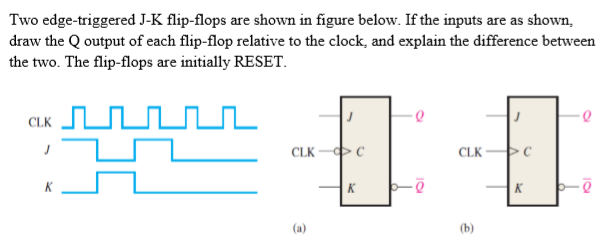

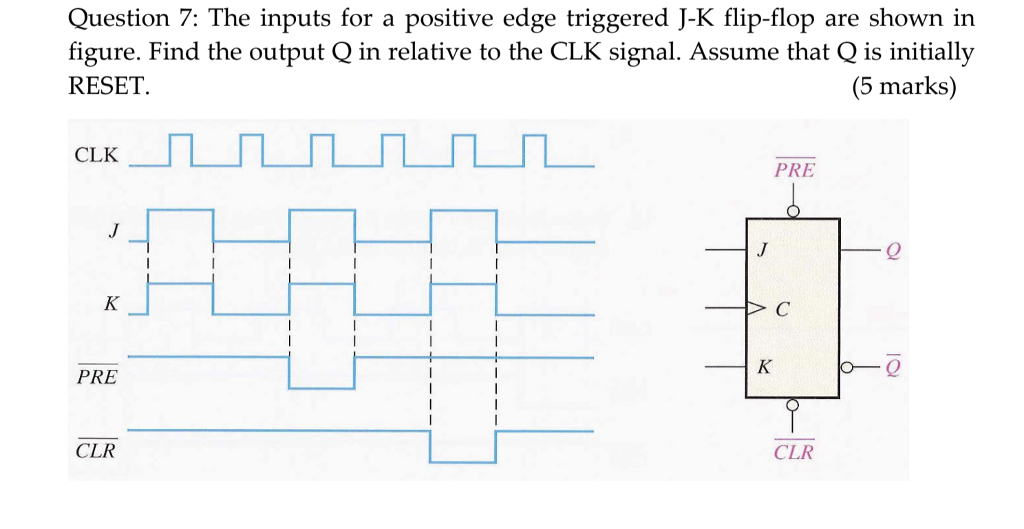

Flip-flops. Outline Edge-Triggered Flip-flops S-R Flip-flop D Flip- flop J-K Flip-flop T Flip-flop Asynchronous Inputs. - ppt download

digital logic - Edge triggering seems to me leaving every circuit in an inconsistent state? - Electrical Engineering Stack Exchange